## Open ISAs, Hardware

and the Numerous Innovation Opportunities

### OpenPOWER ISA

### **OpenPOWER ISA**

- IBM 801 was one of the first RISC computers

- RISC System/6000 (1990) introduced POWER ISA

- IBM + Apple + Motorola (AIM Alliance) worked on PowerPC

- Renamed as POWER ISA in 2006

- OpenPOWER Foundation started in 2013

- Latest Spec Version 3.1

### **RISC-V**

- 5th RISC ISA from Berkeley (2010)

- Open right from the beginning

- Maintained and promoted by RISC-V International

- Adopted by SiFive, WD, Nvidia, Microchip, Alibaba, CDAC, IIT Madras

# DAC Experience

### DAC YF

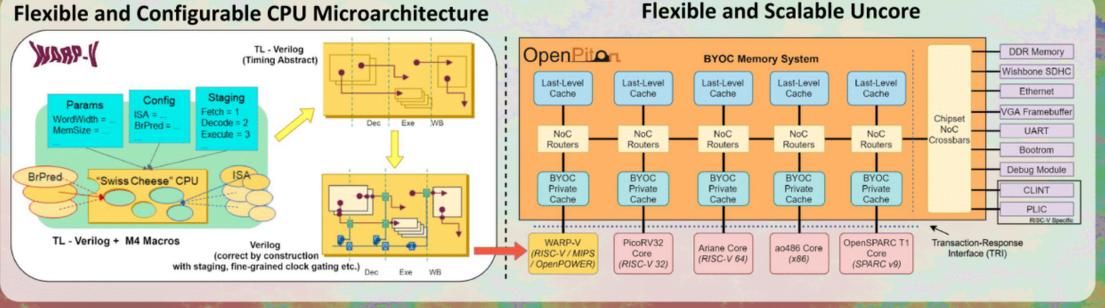

### Flexible Manycore CPU Design with TL-Verilog

Shivam Potdar (YF), Steve Hoover, Jonathan Balkind (Mentors)

# Low-Power

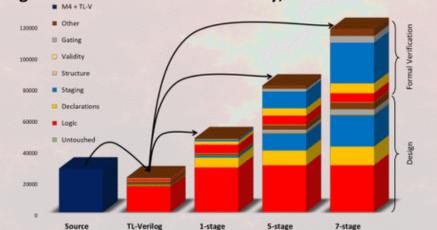

### Huge Code Reduction and Flexibility, but full RTL Control!

#### **Key Takeaways:**

- Demonstrates large-scale design in new Verilog-compatible transaction-level design and formal verification methodology

- Hardware Design, not HLS

- Pipeline staging, clock gating, hierarchy etc. implied

This research is sponsored by Google under Google Summer of Code 2020

# Project Opportunities with OpenPOWER

### **Open Source POWER Cores**

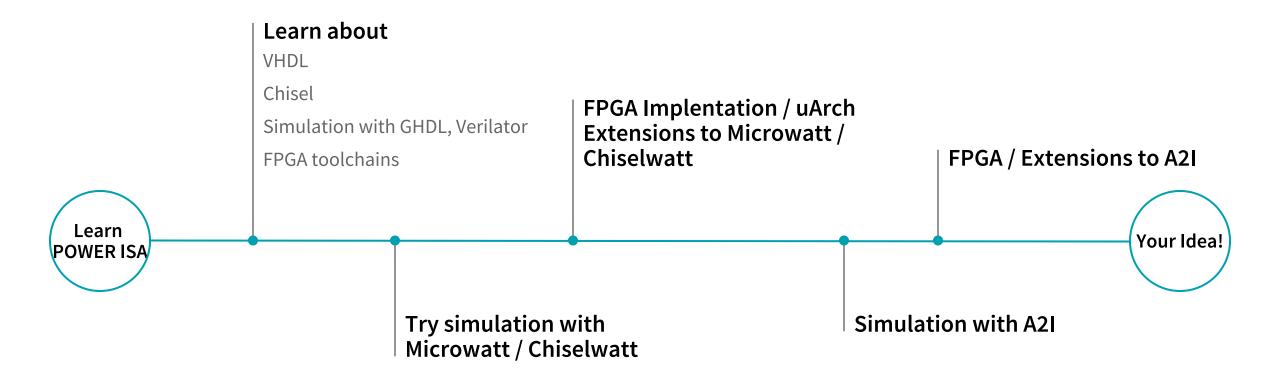

### **Microwatt**

VHDL 2008

**GHDL Simulator**

Xilinx FPGAs (A7)

### Chiselwatt

Chisel

Verilator Simulator

Yosys/nextpnr support for ECP5 based FPGAs

(ULX3S / Orangecrab etc.)

### **A21**

Most powerful open source POWER core at the moment

Used in BlueGene/Q (in many supercomputers even today)

VHDL source

### **Potential Roadmap**

### Resources

- All 3 cores are available on GitHub

- VHDL/ Verilog books and YouTube videos by Brock J Lamares (Free)

- Coursera HDLs for FPGA Design - UC Boulder

- Computer Organization and Design - Patterson and Hennessy

- POWER ISA Manuals

- Verilator, GHDL, Yosys documentation

### **Open hardware in future**

- SoCs

- Heterogeneous systems

- Completely open source RTL to GDS Flow - OpenLane

- Adoption of open standards industry direction

- Worldwide collaboration

- Make in India

### Thank You!

Efforts for OpenPOWER Community being led by -

Mr Ganesan Narayanasamy

Senior Technical Computing Solution and Client Care Manager, IBM

Abhishek Jadhav

BE (EnTC) Senior, FCRIT, Mumbai

Shivam Potdar

BTech (EEE) Senior, NITK Surathkal

30 July 2020 - Shivam Potdar